Parallel Sparse-Matrix Solution

PI: Prof. Yul Chu

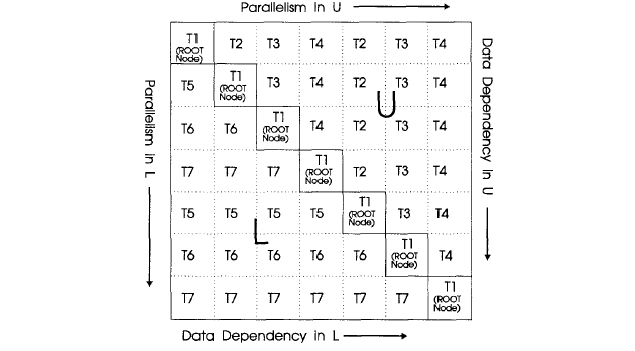

The lab's research focuses on the development of a parallel sparse matrix solution for current high-speed analog and digital VLSI systems. Circuit simulations are based on sparse matrix computations, which have two steps known as the LOAD and SOLVE phases. To improve circuit simulation performance, parallel computations should be exploited for the SOLVE phase since the number of transistors for VLSI systems has been doubled every 18 months. Parallel sparse matrix solutions, known as Parallel SOLVE, have been developed for doing block LU decomposition. The reduction of fill-ins is an important factor in maximizing gains for sparse matrix solutions. The lab is equipped with an NSF funded MRI PC Clusters and is conducting research to reduce loop computations for LU decomposition and matrix multiplication.

The teachers will: 1) write a program to compute Sparse matrix solution using a single-core processor; 2) learn how to do block-partitioning for the program; 3) design parallel matrix computation using multi-core processors based on a block unit of the matrix; and 4) participate in developing more efficient parallel distribution algorithms. The project is suitable for math and technology teachers and will strengthen curriculum in algebra and programming.